低成本工具和成熟工艺让ASIC设计变得简单且经济

2018-07-16 21:33:50 来源:麦姆斯咨询 评论:0 点击:

简介

如今,低成本的设计工具随处可见,灵活成熟的集成电路(IC)工艺也可轻松获取,因此现在是探索专用集成电路(ASIC)优势的绝佳时机。但是,大量文献指出半导体器件开发的成本日臻高涨,会让人觉得只有少数资金充足的初创公司、系统公司或器件制造商才能负担得起ASIC,获得其带来的众多技术优势和商业利益。

打破神话

花逾2500万美元的巨额资金购买一个掩模版,设计成本高达1亿美元,这些传闻使ASIC设计听上去像是一场富人的游戏。但这些数据仅针对那些在个人电脑和智能手机等大规模消费产品中使用的大型片上系统(SoC)器件的前沿技术。物联网(IoT)应用集成度更低,需要与真实世界进行交互,这就要求使用模拟电路。对IoT而言,成熟的“超越摩尔定律”的工艺技术更加合适。这样一来,使用ASIC技术的成本和风险将大大降低。

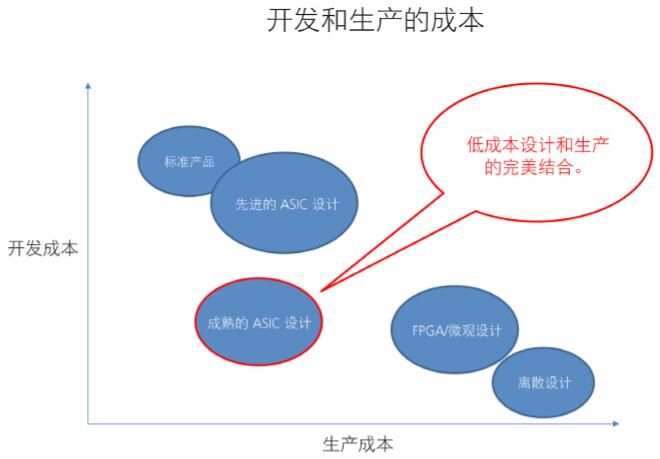

关于成本高涨的传闻沸沸扬扬,但实际上,很多项目的ASIC设计和生产费用越来越低。很多人曾认为只能选择现场可编程逻辑器件(FPGA)或与离散模拟器件耦合的微控制器,不过现在他们发现,专用ASIC设计方法其实更具成本优势,关键在于以下三点:选择合适的设计工具和工艺技术(更重要);利用成本相对较低的成熟的工艺技术;以及运用普及广泛的免费或低成本的知识产权(IP)。图1显示了标准IC产品、ASIC和FPGA等可重构部件的开发和生产成本的关系对比。

图1:各种器件设计的开发和生产成本的比较

ASIC的优势

除了低廉的生产成本,ASIC还具备很多其他的优势。ASIC可以提供更优的性能、更低的功耗、更高的电压、更小的尺寸/物料使用量,从而提高可靠性。还有一点很重要,就是ASIC可以提供更高的IP安全性,因为微控制器或FPGA设计的IP存储在易于读取的内存中,相比之下对ASIC进行逆向工程的难度要大得多。

可复用IP的普及

此外,很多采用成熟AMS工艺的晶圆代工厂提供了各种各样预先表征的IP。这类IP模块在数字领域中的应用已非常普遍。ARM、Imagination Technologies等诸多公司提供了各种功能模块,例如微控制器,其中有很多都适用于混合信号技术,尤其是在物联网应用中。比较器、运算放大器、能隙、模数转换器和数模转换器等模拟电路模块,可以大幅缩短设计时间并减少设计人员面临的风险。

这些较早的工艺还能使用更高的电压,这意味着它们对于要求较高模拟精度的混合信号设计而言是较为普遍的选择。较早的工艺还适用于运行环境需要更高电压的应用,例如汽车、工业控制或电源管理应用。

有些晶圆代工厂甚至可以调整晶圆代工工艺,以满足特定产品或应用的要求。例如,Plessey Semiconductors拥有独特的低功耗工艺,专为心脏起搏器等植入型医疗器械开发,对这些器械而言,电池“寿命”至关重要,甚至是性命攸关的大事!

图2:MPW光刻(来源:MOSIS)

成本分担

通过Europractice等晶圆代工厂提供的多项目晶圆(MPW)服务,可以进一步降低掩模和晶圆生产的成本和风险。如图2(由MOSIS提供)所示,评估/验证或小批量生产需要少量芯片,可以将多个设计合并到单个掩模版中。为专用掩模版投入经费之前,客户通常会订购40个器件用于评估,但单个MPW服务就能针对任何一个设计生产出1000多个器件。MPW成本只是整套专用掩模和晶圆所需成本的一小部分,因为客户只需支付其器件所占晶圆的比例。大部分大型晶圆代工厂都支持多项目晶圆服务。

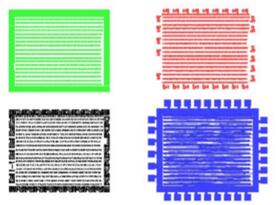

图3:多层掩模(MLM)(来源:XFAB)

XFAB可以进一步减少掩模版生产成本,方法是在同一个掩模中绘制多个工艺层。图3展示了一个掩模的4个工艺层,削减了高达70%的掩模成本。这种方法就是多层掩模(MLM)。

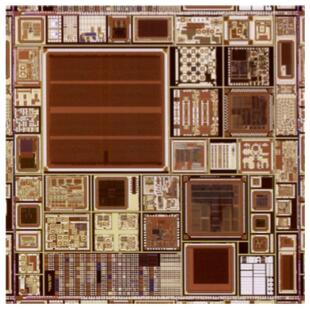

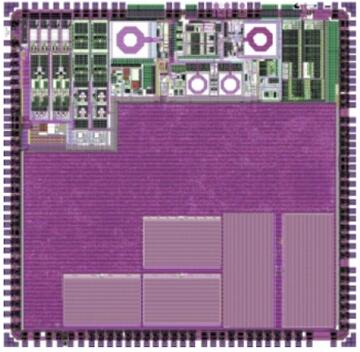

请务必谨记,较早的工艺或MPW服务都不会阻碍尖端的模拟设计。图4展示了20世纪90年代末一家初创公司使用0.35um CMOS工艺开发的第一个单芯片蓝牙收发器。最近,另一家剑桥初创公司正致力于开发新一代通信ASIC,以利用未授权频谱(之前用于模拟电视信号接收,现在可以免费使用),他们既没有采用14nm也没有采用40nm,而是使用至今已成熟的90nm工艺节点。相对较低的晶圆成本加上优良的成品率,不仅保证了该器件在巨量需求应用中能够保持足够低的价格优势,而且也为确保首次设计成功提供了所需的良好的模拟性能和工艺成熟度。

低成本的器件组装和不断普及的测试服务,对制造供应链进行了补充,确保经测试和封装的全功能芯片交付简单、费用低廉。

图4:蓝牙无线收发器(来源:CSR)

低成本设计工具

成熟工艺的运用降低了工具成本。如今已没有必要购买价格昂贵的用于高级纳米级SoC设计的尖端设计工具,因为它们包含很多在成熟节点设计中没有必要的特性。例如,在最近发布的工艺节点,您可能需要一个更复杂和昂贵的设计工具来执行一个拥有数十亿逻辑门的电路设计的仿真、版图布局或验证,而对于工艺成熟的相对简单的混合信号电路是不需要的,因为后者逻辑门的数量也许只在10到1000之间,而且大多数模拟电路都是由晶圆代工厂提供的IP模块,之前已经被多次使用过。

低成本设计工具,如Tanner AMS IC设计流程(过去称为Tanner EDA HiPer Silicon),在上述两个示例中被广泛使用,该工具支持HDL数字设计、综合、布局和布线以及完全自定义模拟设计,使工程师能够经济有效的进行混合信号芯片设计。

对于设计的模拟,低成本甚至免费使用的开源工具拥有高端工具的众多优点,并且去除了任何不必要的功能,从而减少了成本。低成本工具通常易于使用,因为它们没有安装任何不必要的高级功能。但是,这并不意味着它们缺少用于模拟和混合信号设计的高端工具所拥有的功能或能力。图5展示了使用Tanner L-Edit在Cascode镜像版图中对一个节点的高亮显示。

图5:L-Edit图形界面显示了Cascode镜像版图中对一个节点的高亮显示

实现精确、高效设计所需的PDK的易用性,是影响设计工具选择的另一个重要因素。由于业内普遍采用了新兴的互操作PDK或iPDK标准,那就更容易做出选择了。如今,iPDK由大多数晶圆代工厂开发,旨在与所有主要的IC设计工具结合使用。这些iPDK不仅包含与基本工艺相关的数据,例如仿真模型和工艺层,还包括复杂的器件生成宏,即所谓的P-cell(参数化单元)。在过去,大多数工具供应商针对P-cell使用专属语言,因此,晶圆代工厂必须选择支持哪个工具供应商。现在,大多数工具供应商采用Python作为P-cell的语言,这样,晶圆代工厂就可以通过一个PDK支持所有主要工具供应商。

低成本工具本身还有一个优点。持续耗费成本是高端工具的一个主要特征。此类尖端SoC设计流程的设置和维护非常复杂,通常需要专门的CAD部门的支持或签订昂贵的维护合同。如果您与小规模AMS设计团队合作,您需要问问自己,是否有必要承担CAD支持的费用,还是选择更经济的并满足设计需要的工具。

结语

使用低成本设计工具和成熟的工艺,可以实现迅速地投入生产,降低非经常性工程成本,从从而使IC的设计变得越来越容易。如今,您不必再将FPGA或与离散模拟器件耦合的微控制器视为唯一的选择。通过成熟的工艺,您可以将产品设计的关键元素集成到一个集成电路中,从而节约成本并提高性能。定制化的IC不再是那些拥有雄厚财力的公司的专利!

麦姆斯咨询和Mentor建立战略合作伙伴关系,麦姆斯咨询代理销售Tanner系列EDA软件,并开展专题研讨会及培训课程。

联系方式:

麦姆斯咨询

联系人:王懿

电话:17898818163

电子邮箱:WangYi@MEMSConsulting.com

相关热词搜索:ASIC