嵌入式芯片封装发展趋势解析

2018-04-29 10:01:44 来源:麦姆斯咨询 评论:0 点击:

据麦姆斯咨询介绍,芯片及系统外形尺寸的发展趋势是越做越小,嵌入式芯片封装因此找到了新的需求。

根据Yole的报告,日月光(ASE)、奥特斯(AT&S)、通用电气(GE)、新光(Shinko)、太阳诱电(Taiyo Yuden)、TDK、Würth Elektronik等公司都在商业嵌入式芯片封装市场中展开激烈的竞争。事实上,在这场竞争中,ASE与TDK联手合作提高产量。此外,德州仪器(Texas Instruments,TI)和其他集成电路制造商也开发了各自的嵌入式芯片封装。

嵌入式芯片封装与大多数封装类型并不相同。一般来说,在许多集成电路封装中,器件位于基板的顶部。基板充当器件与封装板间“桥梁”的角色。

“嵌入式封装”一词有着不同的含义。但是在嵌入式芯片封装的世界中,指采用多步骤制造工艺将元器件嵌入到基板中。单芯片、多芯片、MEMS或无源元器件均可以并排式(side-by-side)方式嵌入到有机层压基板(organic laminate substrate)之中。这些元器件均通过镀铜的通孔(via)连接起来。总而言之,通过嵌入式封装,就可以释放系统中的空间。

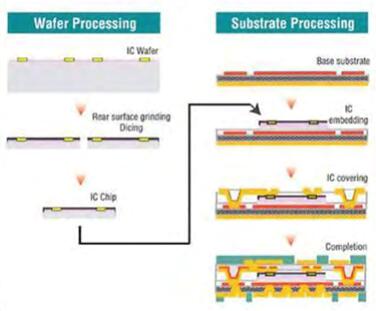

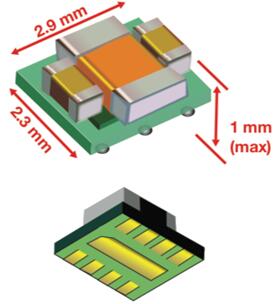

图1:TDK嵌入式芯片封装工艺,称为SESUB(来源:TDK,Prismark)

嵌入式芯片封装并不是一项新技术,可由于工艺中存在各种各样的挑战,这项技术被归为小众应用,但前景光明。例如,TDK最近使用其专有的嵌入式芯片技术,推出了世界上最小的蓝牙模块。此外,嵌入式芯片技术提供了可用于各种应用的多个选项,如微型封装、模块及板上系统(system-in-boards,SiBs)等。

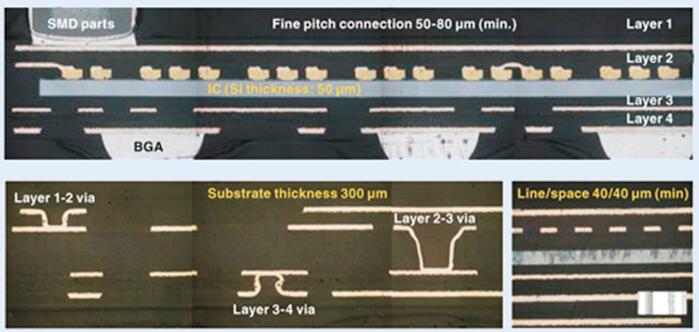

图2:在TDK的工艺中,器件被嵌入四个极薄的基板叠层中,以微互连和通孔为主要特点,总高度为300µm

ASE的工程技术市场营销总监Mark Gerber说:“显然,尺寸是将有源芯片嵌入基板中的驱动因素。在‘x’和‘y’轴上,会显著地整体收缩。当考虑版图布线更大化时,这种微型化可让设计多一些灵活性。如今嵌入式有源元器件的市场,主要围绕着功率模拟器件领域。蓝牙无线模块(Bluetooth WiFi modules)的微型化特点,已成为嵌入式芯片封装的主要应用领域。其他应用还包括手机市场的射频模块。”

嵌入式芯片封装也有缺点。由于它结合了用于先进封装和印刷电路板(PCB)的技术,因此面临一些制造方面的挑战。此外,生态系统还相对不成熟。Yole的分析师Vivienne Hsu解释道:“嵌入式芯片的成本仍然过高,且有时良率太低。”

尽管如此,这项技术还是在多方面取得了进展,为客户提供了另一种选择。事实上,根据Hsu的说法,这项技术与扇出(fan-out)型封装、引线框架封装(leadframe packages)和功率模块(power modules)封装有重叠之处,有时还会相互竞争。

根据Yole的数据,嵌入式芯片封装市场规模仍然较小,2017年至2018年,该市场规模预计将从1500万美元增至1800万美元。到2023年,该市场规模预计将达到5000万美元。

多种封装方式的选择

嵌入式芯片封装是众多集成电路(IC)封装类型中的一种。基本上,IC封装可分为三大类:引线框架封装、晶圆级封装(WLP)和基板级封装。

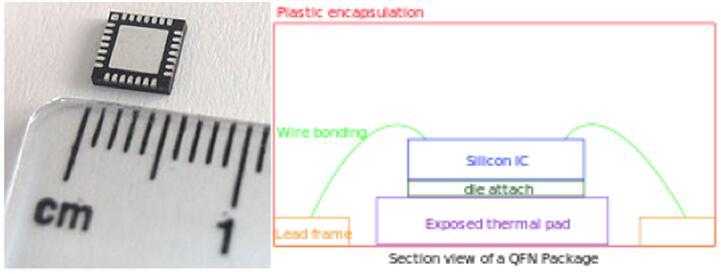

第一类:引线框架封装。用于模拟和其他市场的引线框架封装系列涉及多种封装类型,如方形扁平无引脚封装(QFN)和方型扁平式封装(QFP)。引线框架是金属框架,裸片贴装在框架上,用细引线连接。

图3:QFN封装示意图(资料来源:维基百科)

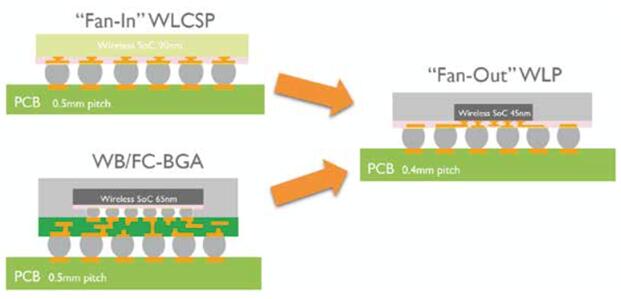

第二类:晶圆级封装(WLP)。这类封装主要涉及扇入型(fan-in)和扇出型(fan-out)两种封装类型。WLP封装时裸片还在晶圆上。一般来说,WLP是一种无基板封装。WLP利用由布线层(routing layers)或重新布线层(RDL)构成的薄膜来代替基板,该薄膜在封装中提供电气连接。

RDL不会直接与电路板连接。相反,WLP会在封装体底部使用锡球,从而将RDL连接到电路板。

图4:扇入型封装、倒装芯片与扇出型封装技术的比较(来源:Yole)

第三类:基于基板的封装。与此同时,基于基板的封装可分为陶瓷基板与有机层压基板等类别。陶瓷基板是基于氧化铝、氮化铝和其他材料制成。基于陶瓷基板的封装通常用于表面贴装器件(surface-mount devices)、CMOS图像传感器和多芯片模块(multi-chip module)。

有机层压基板通常用于2.5D/3D、倒装芯片和系统级封装(SiP)中。这类封装的器件位于基板之上。有机基板的材料通常是FR-4或其他材料。FR-4是一种由环氧树脂组成的玻璃纤维布。这些基板使用类似或相同的材料作为PCB。所以在某些圈子里,有机基板有时就被称为PCB。有机基板也是多层技术,其中至少有两层有机层被金属层隔开。金属层在封装中充当电迁移阻挡层(electromigration shield)。

通常情况下,IC会被封装在电路板上,但这样有时会占用系统中宝贵的电路板空间。因此为什么不把芯片嵌入到基板中以节省空间和成本呢?

这就是嵌入式芯片封装的用武之地,并不会与扇出型封装相混淆。在扇出型封装中,裸片会被嵌入到环氧模压树脂(molded epoxy compound)填充的重新建构晶圆(reconstituted wafer)中。

嵌入式芯片封装是不同的。这些元器件被嵌入到多层基板中。美国TDK的高级战略营销经理Nigel Lim解释道:“IC会被嵌入基板的核心部位。核心部位是用特殊的树脂做的,其他基板层均是标准的PCB材料”。

Lim说:“裸片通常是并排放置的。TDK对并排放置2~3个裸片有着丰富的经验。如果是标准的4层基板,所有裸片都会被放置于2层与3层之间,且裸片不会堆叠。”

这样排列好处较多。AT&S高级封装业务部的首席执行官Dietmar Drofenik和AT&S公司研发部的主任Hannes Vorarberger表示:“ECP技术的主要优点有:促进尺寸微型化、互连可靠、性能更高,并改善了对集成元器件的保护。”AT&S是PCB和基板的供应商,将其嵌入式技术称为嵌入式元器件封装(Embedded Component Packaging ,ECP)。

Drofenik和Vorarberger还补充道:“ECP还支持模块化的趋势,通过降低其他封装技术的成本来实现。隐身的电子器件(嵌入式芯片)可有效防止逆向工程和造假。”

嵌入式芯片是将多个芯片集成到单个封装体中的几种方法之一,但并不是唯一选择。TEL NEXX公司的战略业务发展总监Cristina Chu说:“系统级封装是最受欢迎的选择。由于成本原因,扇出型封装也有很大的发展潜力。正是这些封装解决方案为市场提供价格更低、技术更好的解决方案。”(ASM Pacific已宣布从TEL公司收购TEL NEXX的计划。)

另一个选项是2.5D/3D。所有这些封装类型为客户提供了多种选择。IC供应商可继续根据传统的芯片尺寸的缩小规律来开发片上系统(SoC)产品,此外,只有少数供应商能够负担得起先进节点的设计成本。

另一种获得尺寸缩小好处的方法是将多个器件放在单个先进封装体中,这可能会以较低的成本提供SoC的功能。这就是所谓的异构集成。

为什么嵌入式芯片这么流行?

多年来,这个行业一直以这样或那样的形式来实现嵌入式芯片和无源元器件的封装,嵌入式芯片封装可追溯到上世纪90年代,通用电气(GE)和其他公司推出了该项技术。TechSearch International总裁Jan Vardaman说:“TI的MicroSIP并不是首个嵌入式芯片封装,却是最早那批之一。”

事实上,这项技术是在2010年开始兴起的,当时德州仪器公司(Texas Instruments,TI)推出了其MicroSiP电源模块。该模块将IC嵌入到基板中,其厚度仅为1mm。该产品配置之一是,TI将其PicoStar电源管理器件嵌入到基板中,并将无源元器件安装在封装体的顶部。

TI目前还在销售MicroSiP。TI的Sreenivasan Koduri说:“我们正在将特别设计和制造的PicoStar封装(不是IC)嵌入到基板/ PCB中。电路IP、PicoStar、嵌入芯片与无源芯片集成的组合,实现了价值定位。这就是这项技术得以突破先前解决方案的限制障碍的原因。”

图5:TI MicroSiP的横截面图(来源:TI)

其他公司在竞争中增强自身实力。2013年,GE收购了市场上的领先企业Imbera。2015年,ASE和TDK在竞争中成立了一家合资企业。根据Yole的报告,到2015年,该合资企业中的嵌入式芯片封装业务规模达到了2400万美元。但在2016年和2017年期间,该公司的业务出现了下滑,主要原因是该技术的关键市场(用于移动设备的摄像头模块)增速放缓。

此外,嵌入式芯片的产品设计周期比预期的要长。TechSearch的Vardaman说:“良率是嵌入式芯片的主要挑战之一。”

然而,如今嵌入式芯片封装正呈现新的增长态势。Yole的Hsu说:“这项技术正在逐渐复兴,对数据中心这类有优化热管理需求的行业吸引力巨大。汽车行业对这项技术也有浓厚的兴趣。该技术主要适用于有高功耗(热管理更佳)或超小型(厚度更薄)需求的应用。”

与其他技术相同,嵌入式芯片封装这项技术同样面临着成本、良率和其他问题。Hsu说:“嵌入芯片后,就很难对最终的产品进行测试了。嵌入式芯片的供应链还相对不够成熟。”

其实,该技术还存在其他问题。西门子(Siemens Business)子公司Mentor的产品营销经理David Wiens说:“在PCB空间中,嵌入式无源薄膜元器件(电阻、电容、电感)正在朝超小尺寸发展。额外的制造成本在一定程度上与减少的组装成本相抵消。嵌入式有源器件属于较新的技术,符合小尺寸趋势。由于无法进行返工,注定价格昂贵,而且通常还需要RDL。”

近期,该行业已经采取相应的措施来支持这项技术。几年前,TDK发布了名为半导体嵌入式硅基板(SESUB)的嵌入式芯片技术。TDK已经使用SESUB对包括世界上最小的蓝牙模块在内的产品实现了封装。

然而,SESUB是专属型解决方案。一般来说,客户为确保充足的供货和优质的定价,需要第二个供货渠道。

这也是TDK与ASE共同组建合资企业的动机之一。在合资企业之前,ASE通过两方面参与市场:第一,ASE凭借自己研发的产品;第二,对于那些想要SESUB的客户,ASE就会将设计或元器件发给TDK,TDK会为ASE进行封装。

目前,通过合资企业的方式,ASE可提供整个SESUB的解决方案。该公司已将设备安排在台湾工厂,并正在加紧扩大这项技术的产能。

在基本的SESUB流程中,晶圆在代工厂中加工。晶圆被减薄到50μm,芯片被切割成小块。然后,芯片被放置在单独的面板上,在那里将进行板级(panel-level)工艺。在面板中,我们的目的是加工更多芯片,而不是处理晶圆,以降低成本。

板级工艺也正在为其他市场进行研发。该行业正在以板级的方式开发扇出型封装。这与板级嵌入式芯片封装并不相同。

与此同时,在嵌入式芯片流程中,裸片被贴装在基板的核心位置。裸片会并排放置在其中的一层中。ASE的Gerber说:“那么,最终会在裸片上层压一种材料。然后,回来用激光照射该材料来形成焊盘(pad)。接着,进行图形化工艺再在其上贴装电路板。”

其成果就是将嵌入式芯片的厚度减小到260~300μm。Gerber补充道:“在嵌入式芯片中,可以集成的裸片数量是没有限制的。但大多数情况都将集成芯片的数量保持在4个或更少。因为嵌入的裸片越多,良率损失的风险就越大。”

这项技术有对电热管理有利。Gerber继续解释:“这与正在进行的如TSV的3D堆叠解决方案没什么不同。裸片排列更紧凑,这样互连会更短。当在嵌入式技术上进行互连工艺时,就是在pad的顶部构建了布线层。因此当创建通孔或连接点与pad连接,我发现一种无需焊料就可以实现互连的方法,这就是copper-to-copper。从可靠性的角度来看,如果材料匹配,就不会有太多问题。”

在SESUB中,最通用的配置是4层基板的嵌入式封装,有些也会开发2层、5层或6层的基板。

该技术对于输入输出(I/O)数量的理想数值是400。line/space的规范是大于等于10μm。pad尺寸为80μm,pad间的间距为120μm。Gerber说:“到2018年和2019年,pad尺寸有望会降为30μm,间距降为50μm。”

与此同时,ASE提供了自主研发的名为“先进嵌入式有源系统集成(aEASI)”的嵌入式芯片技术。在近些年的生产过程中,aEASI专为高功率应用提供服务。这是将引线框架和基板技术混合使用的封装技术。

其他选择

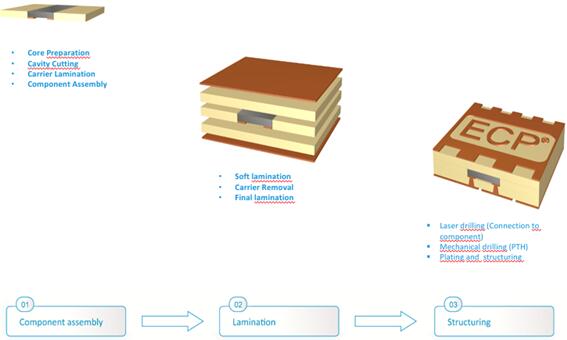

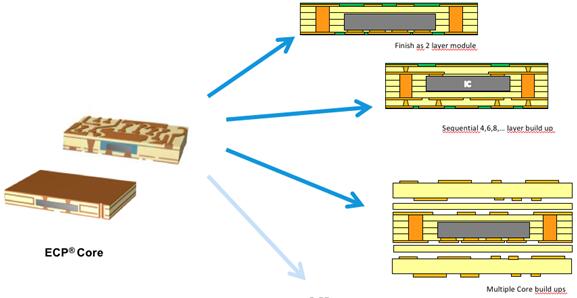

2008年,欧洲成立了将致力于嵌入式芯片技术商业化的联盟。AT&S公司实现了ECP技术的商业化。

AT&S的Drofenik和Vorarberger解释道:“ECP使用有机层压基板中的空间来嵌入有源(芯片)或无源元器件。电容器和电阻器的厚度薄且采用铜布线,已经开发成功,而压敏电阻和热敏电阻还在开发中。”

MEMS也可以集成到封装中。与SESUB一样,ECP也使用板级的方式进行处理。Drofenik和Vorarberger说:“嵌入式工艺可分为三个主要步骤:元器件组装(核心结构、形成空腔、贴保护层)、层压(树脂填充,去保护层)、以及结构化(激光钻孔、电子测试)。”

图6:ECP工艺流程(来源:AT&S)

这项技术可用于汽车、通信、医疗、手机和其他应用。Drofenik和Vorarberger说:“如今,使用这项技术的典型应用有:如穿戴设备、MEMS、无线连接模块等便携式电子设备,如助听器等医疗产品,识别系统或通过扇出技术实现细间距的IC。”

图7:ECP工艺流程(来源:AT&S)

接下来会如何发展?这项技术正朝着AT&S所说的“一体化”模块发展。这正是当今技术的发展趋势。这会涉及使用先进的PCB之类的基板和封装来开发集成度更高、尺寸更小的模块。

为此,客户将有封装一系列新型元器件和技术供选择,包括:绝缘金属基板、多层基板、高密度互连(HDI)、柔性PCB和插入式选项。Drofenik和Vorarberger说:“如先进SIP和SiB等新型先进封装技术,能在很大程度上将所有基本技术以模块化的形式结合起来。”

嵌入式芯片封装前途值得期待!如果能够克服一些挑战,它将会有广阔的发展空间。如果暂时无法克服,它仍是一项利基技术。最坏的情况是,它可能会在混乱的封装技术前景中迷失方向。

延伸阅读:

《先进基板技术及市场现状-2018版:嵌入式芯片和互联、基板式PCB趋势》

《TDK蓝牙(Bluetooth)微型模块:SESUB-PAN-D14580》

推荐培训:

2018年5月25日至5月27日,麦姆斯咨询主办的“MEMS封装和测试培训课程”将在无锡举行,培训内容包含:(1)MEMS分立器件封装技术(金属封装、陶瓷封装、塑料封装等);(2)MEMS晶圆级封装技术(晶圆级键合、晶圆级微帽、晶圆级密封、TSV等);(3)MEMS系统级封装技术及器件失效案例分析;(4)典型MEMS器件封装和测试技术:MEMS麦克风、光学传感器、磁传感器、指纹识别传感器、射频滤波器、图像传感器、气体传感器等;(5)MEMS封装键合设计;(6)选修课程:MEMS设计工具Tanner软件及应用(MEMS设计-建模与仿真方法)。

麦姆斯咨询

联系人:彭琳

电话:17368357393

E-mail:penglin@memsconsulting.com