扇出型封装为何这么火?

2017-02-23 11:01:30 来源:麦姆斯咨询 评论:0 点击:

——麦姆斯咨询详解扇出型封装技术

2017年依然炙手可热的扇出型封装行业

新年伊始,两起先进封装行业的并购已经曝光:维易科(Veeco)签订了8.15亿美元收购优特(Ultratech)的协议,安靠(Amkor Technology)将收购Nanium(未公开交易价值)。Ultratech是扇出型封装光刻设备的市场领导者,Veeco此次交易将有助巩固其在先进封装市场的地位,并丰富光刻机台的产品组合。Amkor交易案将带来双赢的局面:对于Amkor来讲,欧洲公司Nanium在内嵌式晶圆级球栅阵列(eWLB)生产中积累了近10年的晶圆级封装经验,收购Nanium将有助Amkor这家美国巨头完善在扇出型封装方面的专业知识;对Nanium而言,作为欧洲最大的外包半导体组装与测试(OSAT)服务供应商,将获得更多的资金和OSAT业内的影响力,因而可以和亚洲龙头企业竞争。

两起并购案预示了在2016年已经热起来的扇出型封装行业将继续保持火热态势。设备商Veeco、封装测试供应商(Amkor、日月光、星科金朋)、晶圆代工厂(TSMC和GLOBALFOUNDRIES)等等都在此布局。那么,究竟什么是扇出型封装行业?扇出型封装有什么独特的优势?麦姆斯咨询在下文中为你做一个全面的解释。

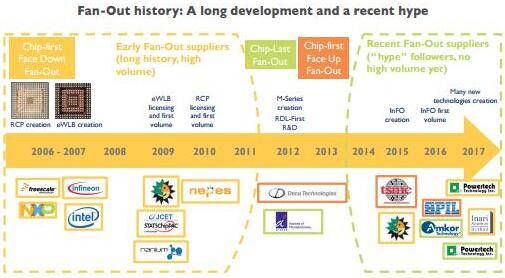

七年发展之路,台积电成功量产InFO带来了扇出型封装的“春天”

2009-2010年期间,扇出型晶圆级封装(Fan-Out Wafer Level Packaging, FOWLP)开始商业化量产,初期主要由英特尔移动(Intel Mobile)推动。但是,扇出型晶圆级封装被限制于一个狭窄的应用范围:手机基带芯片的单芯片封装,并于2011年达到市场极限。2012年,大型无线/移动Fabless厂商开始进行技术评估和导入,并逐步实现批量生产。

2013-2014年,扇出型晶圆级封装面临来自其它封装技术的激烈竞争,如晶圆级芯片尺寸封装(WLCSP)。英特尔移动放弃了该项技术,2014年主要制造商也降低了封装价格,由此市场进入低增长率的过渡阶段。

2016年,TSMC在扇出型晶圆级封装领域开发了集成扇出型(Integrated Fan-Out, InFO)封装技术用于苹果iPhone 7系列手机的A10应用处理器。苹果和TSMC强强联手,将发展多年的扇出型封装技术带入了量产,其示范作用不可小觑,扇出型封装行业的“春天”终于到来!

扇出型封装技术的发展历史

扇出型封装技术及优势详解

从技术特点上看,晶圆级封装主要分为扇入型(Fan-in)和扇出型(Fan-out)两种。传统的WLP封装多采Fan-in型态,应用于引脚数量较少的IC。但伴随IC信号输出引脚数目增加,对焊球间距(Ball Pitch)的要求趋于严格,加上印刷电路板(PCB)构装对于IC封装后尺寸以及信号输出引脚位置的调整需求,扇出型封装方式应运而生。扇出型封装采取拉线出来的方式,可以让多种不同裸晶,做成像WLP工艺一般埋进去,等于减一层封装,假设放置多颗裸晶,等于省了多层封装,从而降低了封装尺寸和成本。各家厂商的扇出型封装技术各有差异,在本文以台积电的集成扇出型晶圆级封装(integrated fan out WLP,以下简称InFO)进行详细介绍。

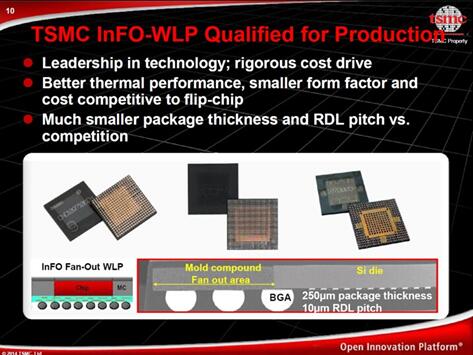

台积电在2014年宣传InFO技术进入量产准备时,称重布线层(RDL)间距(pitch)更小(如10微米),且封装体厚度更薄。

台积电InFO技术实现封装厚度250um,RDL间距10um

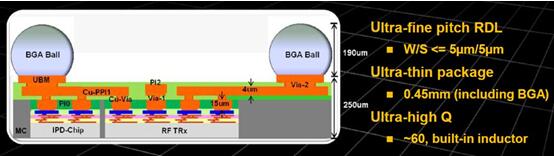

台积电InFO剖面图

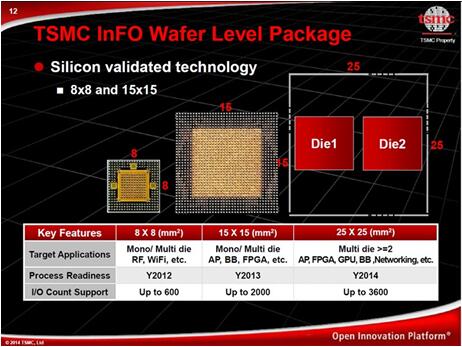

InFO给予了多个芯片集成封装的空间,比如:8mm x 8mm平台可用于射频和无线芯片的封装,15mm x 15mm可用于应用处理器和基带芯片封装,而更大尺寸如25mm x 25mm用于图形处理器和网络等应用的芯片封装。

InFO适用多种可穿戴类设备

相比倒装芯片球栅格阵列(FC-BGA)封装,InFO优势非常明显。对于无源器件如电感、电容等,InFO技术在塑封成型时衬底损耗更低,电气性能更优秀,外形尺寸更小,带来的好处则是热性能更佳,在相同的功率分配下工作温度更低,或者说相同的温度分布时InFO的电路运行速度更快。

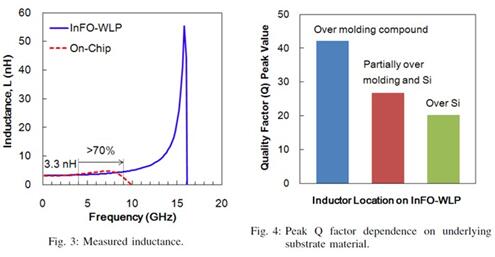

在InFO技术中,铜互连形成在铝PAD上,应用于扇出型区域以制造出高性能的无源器件如电感和电容。与直接封装在衬底的片式(on-chip)电感器相比,厚铜线路的寄生电阻更小,衬底与塑封料间的电容更小,衬底损耗更少。以3.3nH的电感为例,65nm的CMOS采用on-chip封装方式其品质因子Q为12,而InFO封装则可达到高峰值42。电感与塑封料越接近,损耗因子越小,Q值越高。当然,如果电感直接与塑封料接触,性能最佳。

电感采用on-chip和InFO封装的性能比较

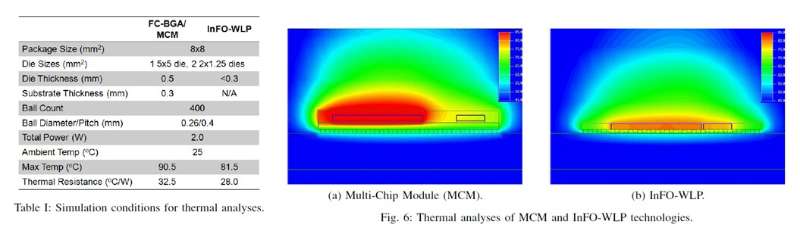

我们来看看多芯片FC-BGA封装方式和InFO封装方式的比较。封装尺寸为8mm x 8mm,内有一个5mm x 5mm的基带芯片,2个2mm x 1.25mm的小芯片,环境温度为25˚C,功耗为2W,符合典型移动系统的要求。InFO封装方式显示出了明显的热性能优异性。InFO封装方式中“消失的”的基板层减小了整体尺寸,切断了芯片通往基板的热流通路径。总体来讲,InFO封装方式的热电阻比传统多芯片组件(MCM)低约14%。(前者为28.0C/W,后者为32.5C/W),从而带来最大达9˚C的温度差异。

InFO WLP与FC BGA MCM热性能比较

60GHz毫米波通信系统允许高清视频流和快速文件传输,已经吸引了千兆数据传输应用。低温共烧陶瓷技术(Low Temperature Co-fired Ceramic LTCC)和PCB基板用于集成毫米波天线与射频芯片,但芯片通过凸块或焊球连接到天线中出现较高的互连损耗,功耗问题是主要的难点。

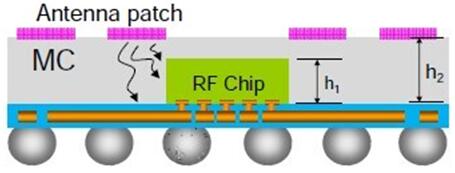

宽带贴片天线采用InFO封装缘由其低介电常数和厚基板的使用。57~64GHz可以选择介电常数为4、厚度为300um(下图中h2)的塑封料(MC)。结构为两层RDLs之间夹一层MC。一层是位于MC顶部的贴片式散热器,其尺寸890(W)um x 1020(L)um;另一层是位于MC下面的馈电结构,嵌入在聚合物之中。

采用InFO封装方式的宽带贴片天线

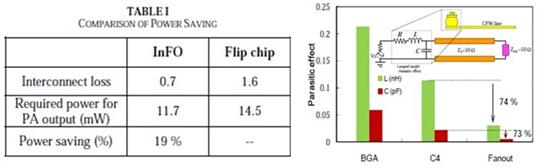

从下面的图表可以看到,倒装芯片的功率放大器输出功率为14.5mW,而采用InFO封装则低至11.7mW,节省了17%的功耗。

一般来说,寄生效应越小,互连损耗越低。下图的右图显示了不同封装方式的集总电路模型的电感和电容。可以清楚地看到,使用铜通孔的扇出型封装寄生效应更小。与C4(Controlled Collapse Chip Connection,可控塌陷芯片连接)相比,减少70%的电感和73%电容,充分说明了扇出型封装的损耗是低于BGA和LTCC基板凸块封装的。

InFO、倒装芯片和BGA三种封装方式比较

到此,你是否get到了扇出型封装的知识?如果还有进一步学习的想法,可以报名参加由麦姆斯咨询在今年5月份组织的《MEMS封装和测试培训课程》,也可以购买相关报告了解更多的产业知识和技术动态。

推荐培训课程:

延伸阅读:

注:麦姆斯咨询正开展专利运营服务,目前已经拥有一批高质量专利,如果您有先进封装(如晶圆级封装和MEMS封装)相关专利需求,欢迎联系我们,邮箱:wangyi#memsconsulting.com(#换成@)。

上一篇:离子束溅射制备低应力深紫外光学薄膜

下一篇:三氧化二铬薄膜的制备及应用