利用Calibre转换并改良IC设计流程

2018-07-02 15:32:20 来源:麦姆斯咨询 评论:0 点击:

简介

Tanner IC设计流程提供了一个完整的从原理图输入、混合信号仿真到全芯片组装和物理验证的自顶向下的解决方案。将Calibre®集成到此设计流程中,使您有信心利用所选晶圆代工厂的最新技术成功地进行设计流片。在Tanner设计环境中,您只需点击相关按钮,即可进行以下互动:

• CalibrenmDRC™(层次化设计规则检查):确保您的物理版图顺利投产制造。使用晶圆代工厂准确且经验证的规则集,为完成物理验证(Signoff)快速调试违规情况。

• CalibrenmLVS™(层次化版图与原理图对比):可从电气和拓扑的角度检查物理版图与原理图是否完全一致。CalibrenmLVS提供了实际器件的几何图形测量、可编程电气规则检查和复杂的交互式调试功能,以确保电路验证准确。

• CalibrexRC™(寄生参数提取):验证版图的寄生参数不会影响设计的电气性能。CalibrexRC可为全面的布线后分析和仿真提供准确的寄生数据。

Calibre是IC验证和Signoff验证的绝对市场领导者,占据了大量的市场份额,可提供准确可靠的解决方案,确保成功进行流片。所有大型晶圆代工厂都使用CalibrenmDRC进行工艺开发和验证。这意味着Calibre规则集已久经验证,可随时供您使用。CalibrenmLVS提供了世界级硅片交付所需的可靠器件识别精度和及时快速的执行能力。此外,所有大型晶圆代工厂都根据领先的工艺描述定义了CalibrexRC的提取规则。

流程了解

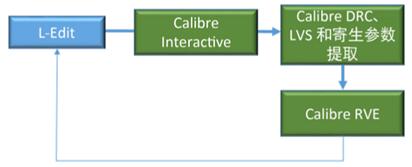

使用L-Edit定义设计版图时,可以通过Calibre工具栏执行设计规则检查(DRC)、原理图和版图比对(LVS)或寄生参数提取(图1)。运行后,Calibre RVE™可提供图形化调试环境,使您可以追踪和修复任何问题。

图1:Calibre流程

运行和使用Calibre Interactive

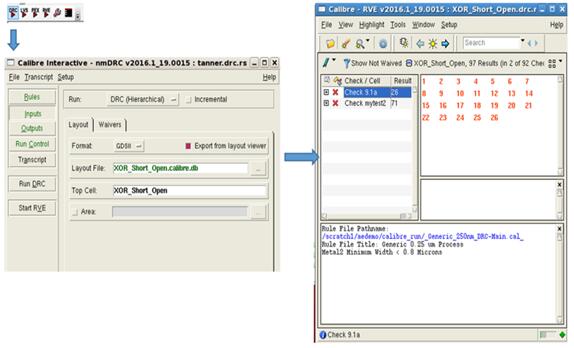

L-Edit中的Calibre工具栏可调用Calibre Interactive以进行DRC、LVS或寄生参数提取。L-Edit会根据您的当前版图预填充对话框。例如,图2中显示的DRC运行。

图2:DRC运行示例

利用Calibre Interactive,您可以在运行所选的Calibre工具前,先设置工具、定义输入和输出并指定选项。

调试DRC违规

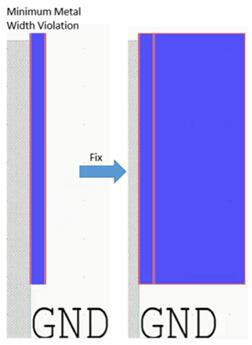

根据晶圆代工厂工艺数据定义的规则,您的物理版图可能存在违规情况,会妨碍设计的成功制造。例如,金属宽度可能太小。点击Calibre RVE中的违规,您便能在L-Edit中高亮显示违规的位置。图3显示的是一种金属宽度违规,您可以通过调整大小来进行更正。

图3:检测金属宽度违规并予以解决

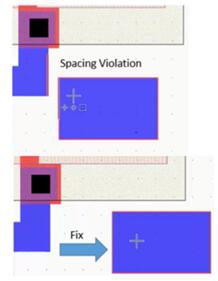

另一种常见DRC违规是由于版图元件之间的间距不正确造成的。例如,图4中显示的两个金属多边形间的间距违规。将一个多边形移到其他位置即可解决此违规。

图4:检测间距违规并予以解决

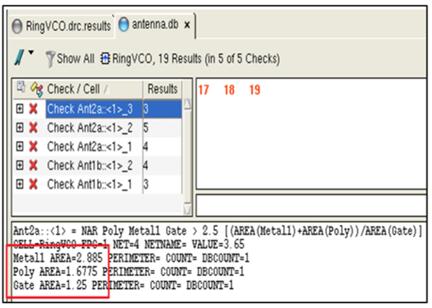

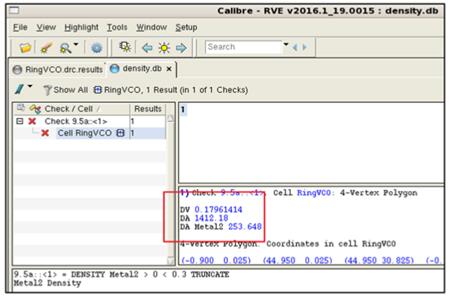

您可以在RVE的辅助数据库中查找其他信息,以便快速修正违规情况。例如,您可以报告其他统计信息,比如每一层的面积和周长,从而帮助修正天线和密度违规(图6)。图5显示的是基于每个网格排列的违规天线报告。您可以缩短与较高金属层连接的天线路径或通过将二极管连接到网络中来解决此违规问题,通过报告中的面积信息,您可以了解及推算需要缩短的天线路径是多少。

图5:天线报告显示其他的统计信息

图6:密度报告显示计算出的密度值(DV)、窗口面积(DA)和金属密度(DA Metal2)

调试LVS问题

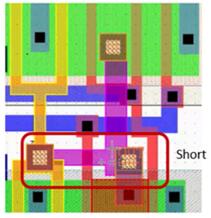

启动CalibrenmLVS将您的原理图和版图发送到Calibre工具进行分析。它能够通过提取过程以及原理图与版图的对比分析来揭示版图错误。例如,提取过程可以显示短路错误。图7显示了一个在版图输入和输出端口之间检测到的短路错误。要解决这一问题,应移除导致短路的金属。

图7:LVS检测到短路错误

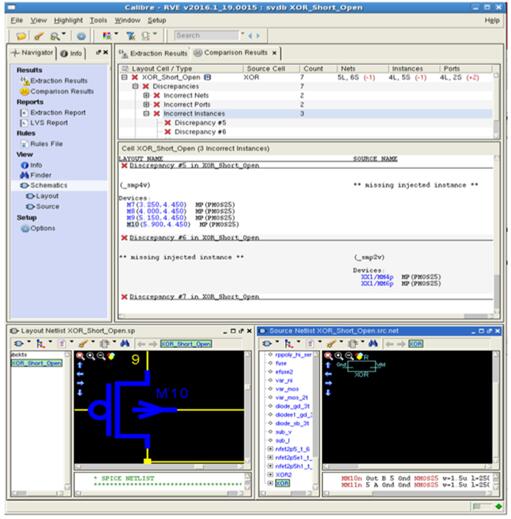

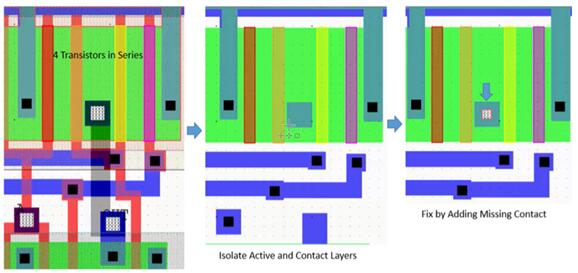

图8显示了LVS的对比结果。在原理图中,有两对串联的晶体管,但是版图中显示这四个晶体管全部串联在一起,因而导致原理图和版图之间的不匹配。本示例中,版图中存在需要审查的问题。

图8:LVS对比结果

图9显示,利用L-Edit功能来打开和关闭图层,然后可以同时查看有源区和接触孔,从而将有问题的部分隔离出来。本示例中,源极到漏极缺少一个接触孔。添加一个接触孔即可解决问题。

图9:LVS违规实例

执行寄生参数提取

从L-Edit工具栏启动用于寄生参数提取的CalibrexRC,可以指定您希望工具执行的提取类型。例如,您可能只想提取电阻(R)或只提取电容(C)或者两者都提取。启动运行时,Calibre首先会执行LVS分析。因此,如出现任何LVS错误,应首先解决这些问题,然后重新运行xRC。您可以在Calibre RVE中查看结果。

提取运行成功后,可以将CalibrexRC生成的SPICE网表文件拖放到T-Spice中,以便分析所提取数据的影响。典型的分析包括检查延迟影响、关键网络的寄生效应以及功耗问题。

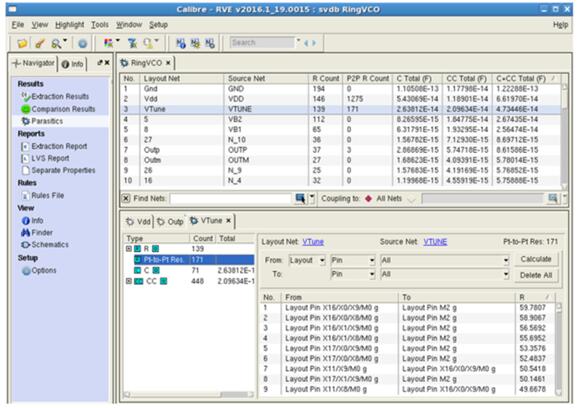

您可以在Calibre RVE中查看寄生效应报告(图10),并根据网络、电阻值或电容值对结果进行排列。双击条目可以计算特定网络的点对点电阻,并在L-Edit中高亮显示电阻路径。

图10:Calibre RVE中的提取结果

结语

Tanner设计流程与Calibre的整合能为您的设计提供世界级的IC验证解决方案。您可以利用各大晶圆代工厂的规则集来检测版图中的问题,将版图与原理图进行比较,从而检测出问题,然后运行寄生参数提取以进行布线后分析和仿真。在设计流程中使用Calibre,您将能更有把握实现成功的流片。

麦姆斯咨询和Mentor建立战略合作伙伴关系,麦姆斯咨询代理销售Tanner系列EDA软件,并开展专题研讨会及培训课程。

联系方式:

麦姆斯咨询

联系人:王懿

电话:17898818163

电子邮箱:WangYi@MEMSConsulting.com

上一篇:Tanner助力Instantaneous实现世界首款瞬时锁定环设计

下一篇:工业物联网(IIoT)——硅谷面临哪些机遇?