Teledyne DALSA引领集成3D MEMS的发展方向

2013-01-11 15:21:00 来源:Teledyne DALSA 评论:0 点击:

作者:邹阳

销售经理,半导体代工业务

Teledyne DALSA Semiconductor

电话: +1 450-534-2321 分机.1220

18, boul. de l'Aéroport, Bromont, QC, Canada , J2L 1S7

关键词:铜TSV,晶圆级封装(WLP),3D集成MEMS

Teledyne DALSA是世界上最专业的MEMS、高压CMOS和先进CCD 制造商之一。过去的几十年研究、创新和工艺开发的丰富经验使我们能够为客户将设计迅速、顺利地转化为量产,帮助客户获得真正的竞争优势。

Teledyne DALSA是全球领先的纯MEMS晶圆代工服务提供商,我们MEMS代工业务的客户遍布美洲、欧洲和亚洲,产品应用涵盖了汽车、工业、通讯、医疗和消费电子市场等。

我们目前主要代工的MEMS产品有MOEMS、惯性传感器、压力传感器、MEMS麦克风、微流体器件、生物MEMS和射频MEMS等,同时我们也提供HV ASIC,如光学MEMS的HV Driver IC。我们在8寸和6寸都拥有可观的产能,可以满足各种量产需求。

近几年亚洲的MEMS应用市场的迅速发展有目共睹,我们相信这主要得益于MEMS产品设计和制造工艺的长足进步使得MEMS产品可以满足市场对性能和成本的要求,特别是消费电子市场的巨大需求推动了惯性传感器、MEMS麦克风的成本迅速降低,使得消费电子市场可以接受。但是现有市场也对现有MEMS产品和供应商也提出了严峻的技术和商业挑战:如消费电子领域对MEMS的芯片尺寸、功耗和精度的要求不断提高对MEMS封装技术提出了挑战;消费电子市场的价格要求给MEMS设计制造和封装测试带来了压缩成本的挑战。

MEMS厂商怎样来应对这些挑战呢?

多年的MEMS代工经验使得我们深刻了解MEMS 的物理和材料学原理,同时我们也一直关注MEMS应用市场的需求。我们相信在未来的很长一段时间内,解决上述问题的的最佳方案是晶圆级封装(Wafer Level Packaging),也就是晶圆级的MEMS和ASIC的3D封装。

晶圆级3D封装具有更小封装尺寸与更高电气性能表现,简化或省略了晶圆制造、封装和测试流程中的若干环节从而可以降低整体和芯片生产成本。

Teledyne Dalsa在优化的制造策略方面有多年丰富的经验,特别在比如通过叠加电路降低封装尺寸,结合 MEMS 与 CMOS 晶圆来实现3D集成器件这些方面。凭借在 3D 和晶圆级封装技术方面的经验,包括通过硅通孔和各种键合技术,Teledyne DALSA 可以帮助客户突破传统设计的限制。

在我们的一些制程平台上比方说200mm Inertial Sensor平台,我们已经是为晶圆级封装做好了准备。

下面我想用一些篇幅来介绍Teledyne DALSA的工艺:

Teledyne DALSA提供给客户一个制程工具箱,包括了几十种可靠、荣获专利的制程模块和技术。

我们提供关键性的表面和体硅微加工技术,包括高深宽比和高速度DRIE,1:1 深宽比时蚀刻深度最高可达 875 µm,蚀刻速度最高可达 40 µm/min。在低温/高导现场掺杂多晶硅用作结构材料和 TSV 技术方面,我们处于领先地位。对于穿透硅互连TSV,我们的 DRIE 能力包括支持 23:1 宽深比和 90-91° 角度,蚀刻速度可达 9 µm/min,并且支持侧壁粗糙度<90 nm、宽深比最高为 35:1 的精细蚀刻,并可控制垂直角度(89.7-90.3°) 和倾斜度(<0.5°)。我们还支持其他角度如 60°,为各向异性湿法蚀刻提供另一种备选方案,从而提高产能和设计灵活性。

图1 硅深反应离子蚀刻(DRIE)

我们使用专有的无水HF释放配方消除蚀刻后粘滞和衍生残留物。低应力SiN是我们的另一项专长(机械应力 = 175 MPa, 耐压强度>4.8 MV/cm),它在无水HF释放期间起到保护作用,并且作为结构材料结合其他硅特性平衡应力。

图2 无水HF释放,专利方法消除粘附和残留物

图3 低应力SiN

机械应力 = 175 MPa;耐压强度>4.8 MV/cm

图4 原位掺杂聚合物ISDP

电阻率 0.65 µOhm•cm

ISDP 应力 = -25 MPa

变化率 = 3.0 Mpa/µm

图5 厚聚合物(涂层厚度:<40 µm; 深宽比 5:1,1至 2 µm 特性)

图6 低温 SiO22,PECVD,SOG

低温 SiO2: 300 nm – 1 µm

PECVD: 100 nm – 10 µm

FH完全释放

SOG: 100 nm to 2.0 µm;高频快速释放

键合是我们的专长领域之一,我们可进行多种技术整合,全面的技术方案包括 Si-Si,Si-SiO2,SiO2-SiO2、熔合、焊接、热压缩,玻璃封接,阳极键合、真空、等离子辅助、聚合物和临时键合。

图7 晶圆键合

图8 金属和镀层

AlCu、AlSiCu、Ti/TiN、Ge、Cu、Ni、Pd、W 及其他

铝基片上的化学镀镍和钯镀层

图9 研磨和切割

薄膜到底层30 µm

焊盘露铜步骤

机械释放结构的切割,无需顶盖晶圆

我们独有的制程工具箱还包括凸点制备(包括 Ni/Pd UBM)、CMP,背面研磨和切割。铝薄膜上的化学镀镍和钯镀层支持同一表面上的可焊接和线焊镀层灵活性,并且支持与其他晶圆进行锡基键合。

晶圆级封装(Wafer Level Packaging)和3D集成MEMS

TSV是3D集成MEMS的关键技术。通常TSV可以分为“Via-First”或者“Via-Last”两类,两者之间主要的区别是“Via-First”TSV是在Bonding之前从而可以承受几百度的高温;而“Via-Last”TSV工序是在Bonding之后,必须在足够低的温度下进行,以防止损坏后端CMOS层。

Teledyne DALSA 的Via-First TSV技术可以利用沟槽填充(in-situ doped poly原位掺杂多晶硅)作为导体,或者,如果需要较大的通孔, MEMS芯片本身可以作为导电区,这时沟槽仅用于提供电隔离。在150mm和200mm晶圆上我们都可以提供这项技术。

图10 原位掺杂聚合物填充沟槽

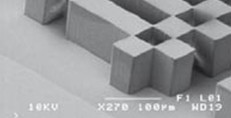

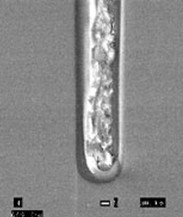

更进一步,在200mm晶圆上Teledyne DALSA 的Via-First TSV技术将采用铜通孔填充,这个技术使用的是Alchimer的低温电化学制程。该技术生产出仅5微米直径,100微米深的完美填充的通孔,利用铜重分布层和Ni / Au UBM作为与外界的导电连接。

图11 5μm 铜填充沟

铜填充工艺阻抗更低、散热更好,可提高运行频率和功率密度,是我们现有的Via-First低阻抗原位掺杂聚合物填充工艺(430 µm 深度典型阻抗< 1 Ohm,电容< 10 pF)的升级。这种新型铜填充工艺十分适合使用高蚀刻速度 Bosch DRIE 工艺进行量产,最高可以将 DRIE 工序成本降低 50%。

图12 硅通孔

Teledyne DALSA开发这个湿镀铜TSV平台的目的是在降低晶圆级MEMS和ASIC之间的封装连接和其他3D封装的成本。我们开发该技术主要目的是为MEMS代工业务客户提供一个标准的TSV平台从而达到降低客户MEMS封装成本的目的,而同时它也可以用来Teledyne母公司的3.4亿美金的数字影像业务提供服务。 Teledyne Dalsa在这个平台上已经优化了设计规则从而减少总的TSV和填充成本,将把它作为一种标准的技术平台提供我们的客户。

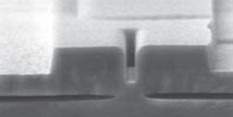

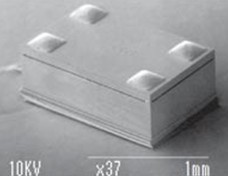

Teledyne DALSA提供的晶圆级 3D 封装方案,使用晶圆级封装大大减小封装尺寸和外观尺寸并且降低成本,是移动应用的理想选择。 Teledyne DALSA 的先进 I/O 方案包括用于叠晶片的 µBGA、可焊接盘或标准盘和用于振荡器、压力及图像传感器的封联合封装设计,以及用于射频滤波器、微流体和硅麦克风的非密封联合封装设计。

图13晶圆级封装(Wafer Level Packaging)

作为MEMS纯晶圆代工服务提供商,客户的成功就是我们的成功,我们相信我们的晶圆级封装方案将帮助客户获得成功。

需要了解更多情况,请访问我们的中文网站:http://teledynedalsa.com/semi/Home.aspx?lang=CN

或者直接和我们联系:http://teledynedalsa.com/semi/contact/contact.aspx