感知“利”器|一种晶圆级封装方法

2017-01-11 13:21:55 来源:麦姆斯咨询 评论:0 点击:

工欲善其事,必先利其器。在全球化的今天,专利已不仅仅是创新的一种保护手段,它已成为商业战场中的利器。麦姆斯咨询倾情打造MEMS、传感器以及物联网领域的专利运营平台,整合全产业链知识产权资源,积极推动知识产权保护与有效利用。

封装是半导体产业链非常重要的一环,为芯片工作提供了有力支撑。据市场研究机构Gartner 数据,2015年全球代工市场营收488亿美元,而封装市场营收达到了255亿美元,两者比例约为1.9:1,因此,封装环节市场不容忽视。

封装技术发展的四个阶段

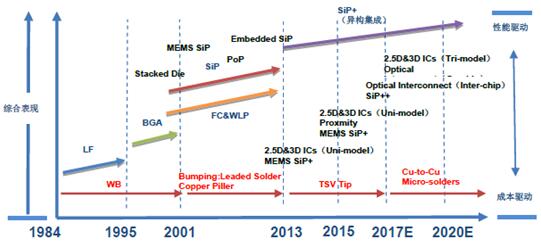

受性能驱动和成本驱动影响,封装技术发展路径大致可分为四个阶段:

封装技术发展路线图

第一阶段为上世纪80年代以前,封装的主体技术是针脚插装;

第二阶段是从上世纪80年代中期开始,表面贴装技术成为最热门的组装技术,改变了传统的PTH插装形式,通过微细的引线将集成电路芯片贴装到基板上,大大提高了集成电路的特性,而且自动化程度也得到了很大的提高;

第三阶段为上世纪90年代,随着器件封装尺寸的进一步小型化,出现了许多新的封装技术和封装形式,其中最具有代表性的技术有球栅阵列、倒装芯片和多芯片组件等,这些新技术大多采用了面阵引脚,封装密度大为提高,在此基础上,还出现了芯片规模封装和芯片直接倒装贴装技术;

第四代封装技术以SiP(系统级封装)、WLP(晶圆级封装)和TSV(硅通孔)为代表,在凸点技术和通孔技术的基础上,进一步提高系统的集成度与性能。

先进封装技术

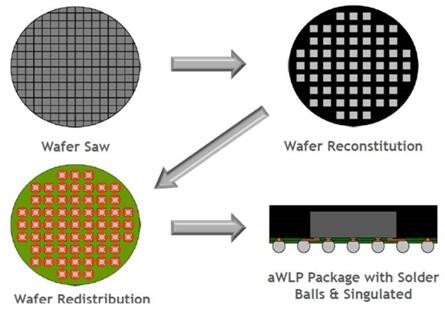

先进封装技术指第四代封装技术,包括SiP、WLP以及TSV等技术,具有尺寸缩小化、引脚密集化与系统集成化等特点。其中,WLP技术直接在晶圆上进行大多数或是全部的封装测试程序,之后再进行切割制成单颗组件,封装尺寸较小。

WLP 晶圆级封装使封装尺寸接近裸片。不同于传统的芯片封装方式(先切割再封测,而封装后至少增加原芯片20%的体积),晶圆级封装是先在整片晶圆上进行封装和测试,然后才切割成一个个的IC颗粒,因此封装后的体积即等同IC裸晶的原尺寸。

晶圆级封装工艺流程

理论上,WLP由于不需要中介层(Interposer)、填充物(Underfill)与导线架,并且省略黏晶、打线等制程,因此能够大幅减少材料以及人工成本;除此之外,WLP大多采用重新分布与凸块技术作为I/O绕线手段,因此WLP具有较小的封装尺寸与较佳电性表现的优势,目前多见于强调轻薄短小特性的可携式电子产品IC封装应用。

知名市场研究机构Yole在其近期发布的报告《中国先进封装产业现状和展望》中预测,在中国半导体市场的强劲增长和政府对先进封装的大力支持下,预计未来几年,中国先进封装市场的复合年增长率为16%,到2020年将达到46亿美元。

中国具备先进封装技术的企业分布情况

【推荐发明专利】

US 7361284-Method for wafer-level package

【技术背景】

本发明关于一种晶圆级封装之方法,尤指一种可提供晶圆级测试,并具有气密视窗的晶圆级封装方法。

对于光学元件与MEMS元件而言,由于光学元件的感光区与MEMS元件的动作空间要求,因此上述元件在封装后通常必须形成一个气密空间或一个可透光的气密视窗,借此除了能够保护元件免于受到空气、灰尘和湿气等影响污染,同时还可以避免元件受到机械力和辐射的影响,以及避免气密空间内灌注的保护气体外泄或真空状态的破坏。由此可知,对于光学元件与MEMS元件而言,构成气密空间或气密视窗的保护上盖决定了此类元件的可靠度。

然而已知的封装方法中所使用的接合胶,如高分子胶,由于热稳定性不良,因此容易影响元件的可靠度,特别是对于气密性要求较高的光学元件和MEMS元件。此外,现有的封装方法是先将元件晶圆切割成复数个元件晶粒后,再开始进行元件的封装,换言之,必须个别地对每一元件晶粒加以封装,甚至必须利用人工方式生产,而此举严重影响了后段封装制程的效率与良率,同时并大幅增加成本。

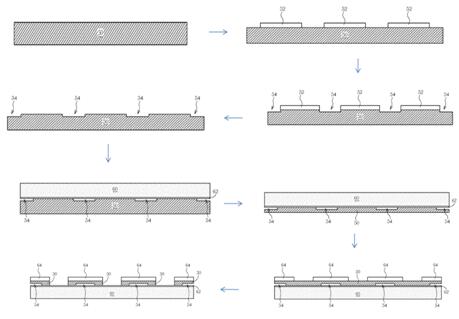

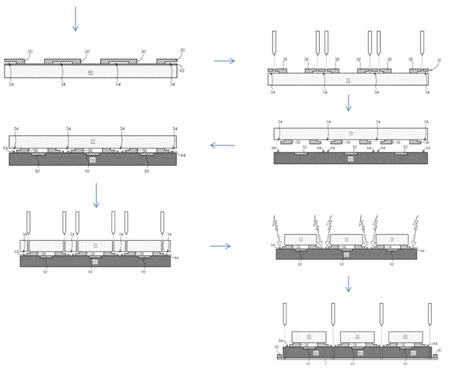

为达上述目的,本发明提供了一种晶圆级封装方法。首先提供一个上盖晶圆,并于上盖晶圆的第一表面形成复数个凹槽。接着将上盖晶圆的第一表面接合于一承载晶圆上,并由该上盖晶圆的第二表面蚀刻该上盖晶圆,以蚀穿该等凹槽周围的该上盖晶圆。随后,将上盖晶圆从承载晶圆上移除,并将上盖晶圆的第一表面与一透明晶圆接合。

再从上盖晶圆的第二表面去除对应凹槽部分的上盖晶圆,以使未去除的上盖晶圆形成复数个支撑块。提供一元件晶圆,其包含有复数个元件及复数个接触垫。最后将支撑块与元件晶圆接合,借此支撑块与透明晶圆可将元件气密封合。

【本发明的优势】

本发明之晶圆级封装方法具有高气密性、高良率及可批量化生产等优点,同时更可提供晶圆级测试,并与一般半导体工艺相兼容等优势。

【其它晶圆级封装相关专利】

US 7045463-METHOD OF ETCHING CAVITIES HAVING DIFFERENT ASPECT RATIOS(蚀刻具不同深宽比之孔洞的方法)

US 7008821-METHOD OF FORMING A WAFER BACKSIDE INTERCONNECTING WIRE(制作晶圆背面内连接导线之方法)

US 7582511-METHOD FOR WAFER LEVEL CHIP SCALE PACKAGING WITH PASSIVE COMPONENTS INTEGRATED INTO PACKAGING STRUCTURE(无源组件集成的晶圆级封装方法及其结构)

US 7598125-METHOD FOR WAFER LEVEL PACKAGING AND FABRICATING CAP STRUCTURES(晶圆级封装与制作上盖结构之方法)

US 7622334-WAFER-LEVEL PACKAGING CUTTING METHOD CAPABLE OF PROTECTING CONTACT PADS(保护连接垫的晶圆级封装切割方法)

专利购买或技术合作请联系:

麦姆斯咨询 殷飞

电子邮箱:yinfei@memsconsulting.com

若需要更多可交易专利,敬请访问:www.mems.me/mems/patent/