Sony三层堆叠式CMOS图像传感器揭密

2017-07-14 19:23:13 来源:麦姆斯咨询 评论:0 点击:

在今年二月举行的国际固态电路会议(ISSCC)期间,Sony宣布推出“业界首款配备DRAM的三层堆叠式CMOS图像传感器”,这款型号为IMX400的三层堆叠式感光元件(Exmor RS)是专为智能手机而打造的。

为了加速图像信息处理,业界多年来一直流传着在互补金属氧化物半导体(CMOS)图像传感器中配备嵌入式动态随机存储器(DRAM)的种种消息,但至今尚未看到任何相关产品投入生产或实际上市。

Sony在ISSCC会议上发表的研究论文揭露了新款感光元件的相关细节,它确实看来像是真有那么回事,这当然马上引起了我们在TechInsights的图像传感器专家们的关注。接着,Sony在其后举行的全球移动通信大会(Mobile World Congress;MWC)确认了该元件的生产状况,并宣布其Xperia XZ Premium和Xperia XZ两款旗舰级智能手机搭载了具有960fps画面更新率的Motion Eye摄像头模组。

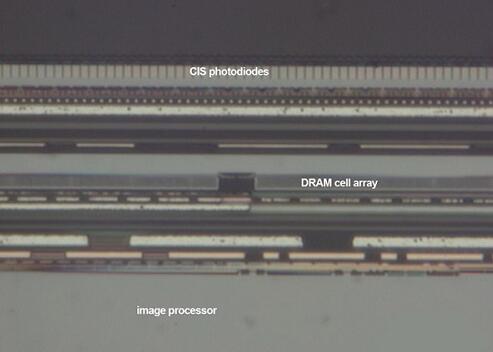

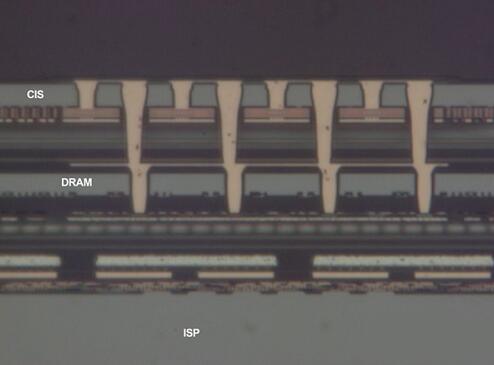

我们尽可能地在Xperia XZ手机一上市就立刻入手,并横切其后置摄像头芯片进行观察。没想到它真的是三层堆叠的感光元件!这款CMOS图像传感器(CIS)被面对背地安装在DRAM上,使得DRAM与图像信号处理器(ISP)面对面接在一起。

图1 Sony三层堆叠式CMOS图像传感器的芯片横截面

然而,我们似乎是超之过急了,因此,让我们先来看看Sony的新闻稿以及在ISSCC发表的论文细节吧!

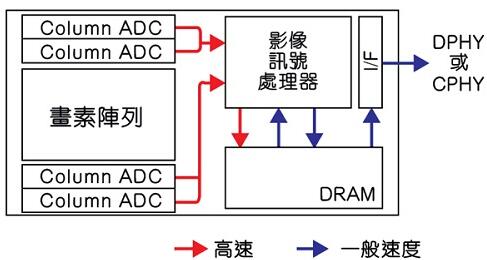

图2 Sony CMOS图像传感器的信号路径方块图

Sony在其较早的1930万像素图像传感器中使用双模拟/数字转换器(ADC),为像素信息进行数字化。而今,该公司使用4层ADC的结构提高读取速度,同时也改善了处理能力。DRAM则用于暂时储存高速资料,然后再以传感器接口的最佳速率输出。该设计使其能以1/120秒读取1930万像素的静态图像,而在影片模式下可达到1000fps的画面更新率,较以往产品的静态图片与动态影片分别提高了4倍和8倍的速度。

由于在CIS和ISP之间加进了DRAM夹层,高速资料必须经过存储器芯片才能到达ISP,然后再以适于应用处理器的常规速度,来回传送直到经由ISP的I/F接口区块进行输出。

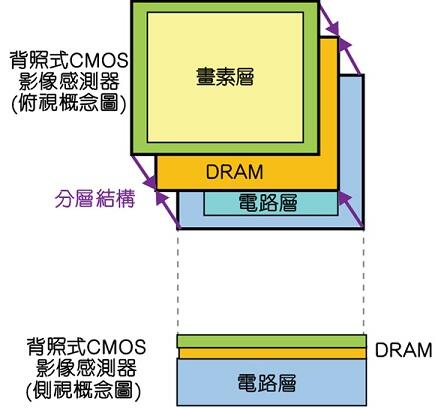

图3 Sony新开发配备DRAM的三层堆叠式CMOS图像传感器

图3是这种传感器运作原理的精简版;但在Sony发表的论文中有更详细的介绍,包括960fps如何成像以及慢动作的工作原理。

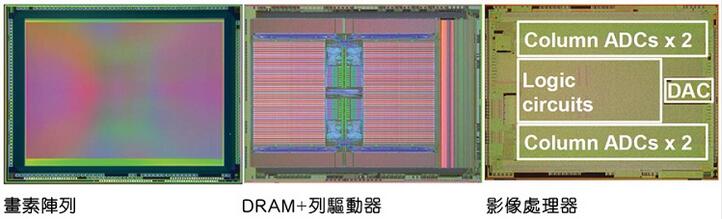

根据该论文解释,像素阵列位于裸晶的顶层,DRAM阵列和列驱动器位于中间,其余的区块则位于底部的ISP裸晶。我们尚未取得这三层裸晶的照片,但该论文中提供了一些图片。

图4 Sony的原理图中显示CIS、DRAM与ISP三层堆叠

Sony并指出,该CIS采用90nm工艺(1 Al / 5 Cu)技术制造,DRAM是1Gb、30nm的(3 Al / 1 W)元件,ISP元件(1 Al / 6 Cu)则采用40nm工艺。要将各种必要的功能加进相同尺寸的3个裸晶,而又不至于浪费芯片面积,无疑是一大挑战。

由于DRAM裸晶上还有CIS列驱动器,因此必须采用定制元件设计,而非我们在近年来看到以硅通孔(TSV)封装的商用DRAM。Sony的芯片横截面图并显示,裸晶中央有一层厚重的氧化物以及适于让TVS从上方CIS向下连接的接合焊垫。

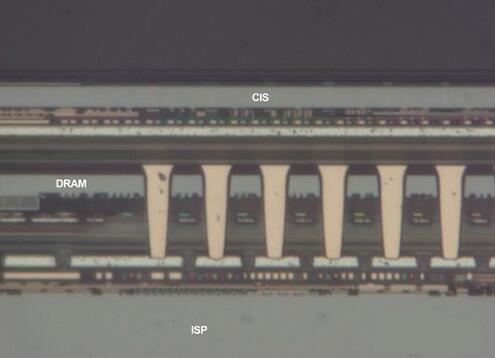

图5 三层堆叠式图像传感器芯片横截面

我们还可以看到(在比例尺准确的前提下),CIS和DRAM裸晶基板已经被削薄至小于2.6μm了,这在背照式CIS(BI-CIS)是十分常见的,但却是我们所见过最薄的DRAM。从我们自己所拍摄的图像(图5)可证实CIS和DRAM的芯片厚度相同,而且也可以看到接合焊垫。

因此,接下来的问题就是——TSV如何在此堆叠中形成?我们的第一款芯片横截面才刚从实验室完成,看起来相当令人熟悉。CIS/DRAM的互连似乎是Sony上一代背照式BI-CIS元件中的TSV形式之一(图6)。

图6 CIS/DRAM互连采用上一代BI-CIS的TSV形式?

此处可看到两层TSV将CIS中看起来像6金属的堆叠连接至DRAM裸晶的M1。我们并未扩展TSV直接连接CIS与ISP的横截面图,不过也存在TSV穿过DRAM连接至ISP顶部金属的情形。

图7 CIS与ISP之间能以DRAM接合点进行连接?

CIS/ISP的连接似乎可以采用DRAM接合焊垫层作为互连,以避免在完整的堆叠形成后还得在两个裸晶间进行钻孔的挑战。

对于IMX400的进一步分析正持续进行中,随着时间的进展,我们很快地就能够掌握有关CIS本身及其封装堆叠的细节。以产业的观点来看,Sony可说是再次将手机摄像头的功能推至极限。不过,在今年稍晚将会出现的一大疑问是——我们将在下一代iPhone中看到这款感光元件吗?

延伸阅读:

相关热词搜索:图像传感器

上一篇:Melexis发布面向汽车、工业和智能城市领域的ToF芯片组

下一篇:松下新款图像传感器有望改善自动驾驶汽车和监控技术

经典文章回顾

- 导远电子推出全新MEMS组合定位系统INS570D,为智能驾驶量产落地保驾护航

- 全球首款单芯片集成ASIC的电容式MEMS超声波换能器(CMUT)

- 豪威科技发布入门级倒车后视SoC图像传感器:OX01E10

- 兵器214所推出12款高性能MEMS惯性传感器

- 矽杰微电子发布24GHz毫米波雷达收发机SOC:SRK1202A

- 青岛芯笙推出多款气体质量流量计和控制器产品

- 解读全球首款MEMS超声波ToF传感器

- TDK推出高性能6轴IMU:ICM-42688-P,适用于机器人、可穿戴及物联网

- 宜普电源(EPC)谈GaN功率器件技术及应用(三):激光雷达

- 灿瑞科技率先推出“ToF光源+驱动IC”整合封装,大力拓展3D传感应用