感知“利”器|三维堆叠相变存储阵列器件及其制备方法

2018-02-26 20:01:40 来源:麦姆斯咨询 评论:0 点击:

工欲善其事,必先利其器。在全球化的今天,专利已不仅仅是创新的一种保护手段,它已成为商业战场中的利器。麦姆斯咨询倾情打造MEMS、传感器以及物联网领域的专利运营平台,整合全产业链知识产权资源,积极推动知识产权保护与有效利用。

半导体存储技术是一种不断更新、进步的技术。据麦姆斯咨询报道,全球存储器行业正处于强劲增长的阶段。预计2016~2022年整个存储器市场的复合年增长率约为9%,市场规模到2022将达到1350亿美元。开发新型半导体存储技术,设计高密度的存储架构是解决现有存储器产品不足之处的有效途径。伴随着半导体工艺节点的逐步缩小,器件尺寸将到达其物理极限,对于高密度海量存储具有一定挑战性。因此,器件设计者已经开始三维可堆叠型存储器结构的研发工作,以达到每个存储位具有更高的存储容量、高可靠性、低工艺成本以及与CMOS工艺兼容性等要求。

独立存储器市场供应链主要厂商

图片源自:《新兴非易失性存储(NVM)市场及技术趋势-2017版》

著名半导体公司IBM称,相变随机存储器(Phase-change Random Access Memory,PCRAM)是一种最有潜力在半导体存储器市场中替代NAND闪存而将成为存储器市场上的主流产品。PCRAM具有两个稳定的相态,即:非晶态(高电阻率)和晶态(低电阻率),通过电脉冲操作,在相变存储单元中实现“0”和“1”的存储。由于其写操作速度与闪存技术相当,较低的静态漏电流、快速读取、易实现高密度存储以及可微缩性等优势,被业界广泛看好。

相变存储器作为高密度存储技术是国际上的研究热点。在过去的十多年中,三星、海力士、旺宏、IBM、美光及英特尔等公司先后开发了多种工艺、多种结构、不同容量的PCRAM芯片。

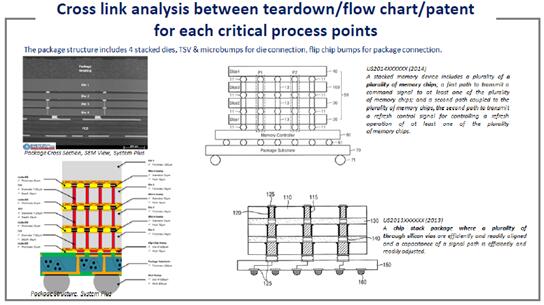

硅通孔堆叠式存储,器件与专利对比分析

随着光刻工艺技术的进一步发展,40nm及以下工艺节点中研发高密度二极管驱动阵列面临巨大的挑战,如:二极管阵列中相邻位线/相邻字线间的串扰,具有高深宽比隔离沟槽的刻蚀与填充工艺,二极管正向驱动电流和反向截止电流的一致性等。在平面工艺中,PCRAM存储阵列密度提升空间有限,那么通过三维立体结构提升PCRAM的存储密度将成为实现海量存储的高效、低成本途径。三维堆叠结构已经应用于其他存储技术中。

对于PCRAM而言,在三维立体结构中实现多层存储阵列的堆叠同样可以有效的提升存储容量并降低工艺成本。

因此,如何提供一种三维堆叠相变存储阵列器件及其制备方法,以降低PCRAM制造成本并提高存储容量及存储密度,成为本领域技术人员亟待解决的一个重要技术问题。

【推荐发明专利】

《一种三维堆叠相变存储阵列器件及其制备方法》

【发明内容】

本发明的三维堆叠相变存储阵列器件的制备方法在驱动阵列上形成相变单元的三维堆叠结构,并采用无结型晶体管作为层控制端(SSL),该制备方法与传统CMOS工艺兼容,其中,无结型晶体管和相变单元的形成均为低温工艺,其热处理制程不会对外围电路造成性能漂移,并且无结型晶体管的沟道采用无浓度梯度的N+型多晶硅材料,有效地避免了离子注入等掺杂工艺引入的额外光罩。

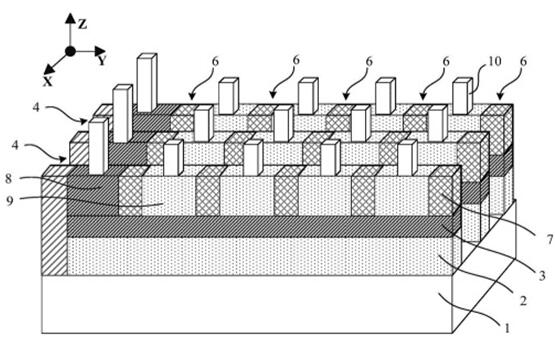

本发明的三维堆叠相变存储阵列器件所采用的一种驱动阵列的立体结构示意图

本发明的三维堆叠相变存储阵列器件中,无结型晶体管的栅极采用控制栅极的阶梯式引出方式,形成SSL控制端,WL、BL和SSL的交界点处有一个相变存储单元,实现对每一个存储位点的读、写、擦操作。

此外,栅极导电材料与绝缘介质层所构成的堆叠结构横跨在相邻的两个钨塞之上,实现了相变材料层的共用,最大程度地降低工艺成本,提升存储密度。本发明的三维堆叠相变存储阵列器件及其制备方法还可以应用于其他存储器件,有效地解决了高密度、嵌入式、海量存储技术的难题。

【相关报告】

专利购买或技术合作请联系:

麦姆斯咨询 殷飞

联系电话:0510-83481111-886

电子邮箱:yinfei@memsconsulting.com

若需要更多可交易专利,敬请访问:www.mems.me/mems/patent/